索尼半导体解决方案公司(下称“索尼”)已成功开发出全球首创*1的双层晶体管像素堆叠式CMOS图像传感器技术。传统CMOS图像传感器的光电二极管和像素晶体管分布在同一基片,而索尼的新技术将光电二极管和像素晶体管分离在不同的基片层。与传统图像传感器相比,这一全新的结构使饱和信号量*3约提升至原来的2倍*2,扩大了动态范围并降低噪点,从而显著提高成像性能。采用新技术的像素结构,无论是在当前还是更小的像素尺寸下,都能保持或是提升像素现有的特性。

*1: 截至2021年12月16日发布时间。

*2: 基于公司之前的图像传感器和应用新技术的索尼背照式CMOS图像传感器之间特性的比较(换算为1um), 截至2021年12月16日发布时间。

*3:单个像素的最大电子存储容量。

索尼在2021年12月11日(星期六)开始的IEEE国际电子设备会议上宣布了这一突破性技术。

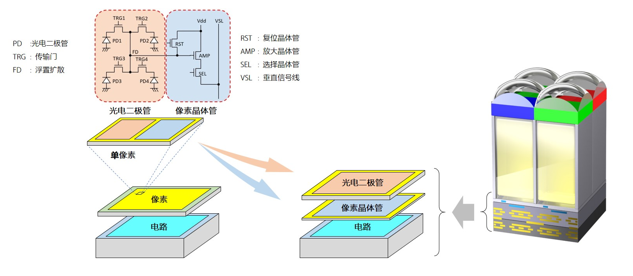

■堆叠式CMOS图像传感器结构

传统的堆叠式图像传感器(左);采用新开发的双层晶体管像素技术的堆叠式CMOS图像传感器(右)

(传统的)堆叠式CMOS图像传感器的堆叠式结构中,背照式像素组成的像素芯片堆叠在逻辑芯片之上,而信号处理电路构成了逻辑芯片。在像素芯片内,用于将光转换为电信号的光电二极管和用于控制信号的像素晶体管在同一基片层并列。在这样的结构限制下,如何实现饱和信号量的最大化,对实现高动态范围、高图像质量的摄影具有重要作用。

索尼开发出的全新结构是堆叠式CMOS图像传感器技术的一项进步。索尼使用专有的堆叠技术,将光电二极管和像素晶体管封装在分离的基片上,一个堆叠在另一个上面。

相比之下,在传统的堆叠式CMOS图像传感器中,光电二极管和像素晶体管并排位于同一基片上。新的堆叠技术支持采用可以独立优化光电二极管和像素晶体管层的架构,从而使饱和信号量相比于传统图像传感器增加约一倍,进而扩大动态范围。

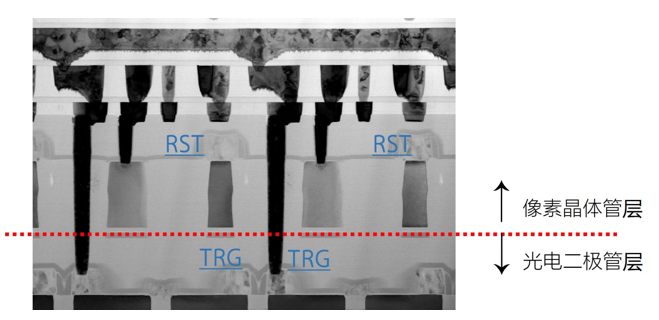

此外,因为传输门 (TRG) 以外的像素晶体管,包括复位晶体管 (RST)、选择晶体管 (SEL) 和放大晶体管 (AMP),都处于无光电二极管分布这一层,所以放大晶体管(AMP)的尺寸可以增加。通过增加放大晶体管尺寸,索尼成功地大幅降低了夜间和其他昏暗场景下图像容易产生的噪点问题。

这项新技术使动态范围扩大并降低了噪点,将避免在有明暗差(例如背光设置)的场景下曝光不足和过度曝光的问题,即使在光线不充足(例如室内、夜间)的场景下也能拍摄高质量低噪点的图像。

索尼将通过双层晶体管像素技术致力于实现更高质量的成像,例如智能手机拍摄等。

采用双层晶体管像素技术的CMOS图像传感器的横截面图片

(本文译自英文新闻稿,供参考)********************************************************************************************

索尼半导体解决方案公司是索尼集团的全资子公司,也是图像传感器领域的全球领导者。我们的半导体业务还涉及种类繁多的部件产品,如微显示设备、大规模集成电路和激光二极管等。我们努力提供先进的影像技术为人们的生活带来更多便利与愉悦。此外,我们还开发并将新的传感技术推向市场,致力于将人类与机器的视觉和认知能力提升到新的高度。欲了解更多详情,请浏览网站:https://www.sony-semicon.co.jp/cn/